# EXPERIMENT NO. 9: DIGITAL-TO-ANALOG AND ANALOG-TO-DIGITAL CONVERTERS

#### 1.0 AIM:

The primary aim of this experiment is to gain a thorough understanding of the working principles, practical implementation, and performance characteristics of Digital-to-Analog Converters (DACs) and Analog-to-Digital Converters (ADCs). This includes building and characterizing a key DAC architecture (R-2R Ladder) and conceptually exploring other DAC and ADC types.

#### 2.0 OBJECTIVES:

Upon successful completion of this experiment, you will be able to:

- Understand DAC Principles: Grasp the fundamental concept of digital-to-analog conversion and the need for DACs in mixed-signal systems.

- Design and Construct R-2R Ladder DAC: Build and test a 3-bit or 4-bit R-2R ladder DAC using discrete resistors and an Op-Amp.

- Characterize R-2R DAC: Measure the analog output voltage for all possible digital input combinations and plot the transfer characteristic.

- Compare DAC Architectures: Understand the principles of a Weighted Resistor DAC (optional implementation) and compare its performance and component requirements with the R-2R ladder DAC.

- Understand ADC Principles: Grasp the fundamental concept of analog-to-digital conversion and the need for ADCs.

- Understand Single-Slope ADC: Comprehend the working principle of a single-slope ADC, including its ramp generator, comparator, and counter components.

- Qualitatively Demonstrate Single-Slope ADC: Implement a basic single-slope ADC (if feasible with available components) and qualitatively observe its conversion process.

- Understand Successive Approximation ADC (SAR ADC): Comprehend the principle of operation of a successive approximation ADC, including its speed advantage.

- Explore Switched Capacitor Integrator (Optional/Advanced): Understand the

concept of switched capacitor circuits and their application in integrators,

comparing them to continuous-time integrators and discussing their

advantages in integrated circuit design.

- Instrumentation Skills: Effectively utilize laboratory equipment such as DC power supply, DMM, and oscilloscope for circuit characterization and verification.

# 3.0 APPARATUS REQUIRED:

A comprehensive list of components and equipment necessary for performing this experiment.

| S.<br>No. | Component/Equipment               | Specifications/Value                                                                            | Quantity                                                        |

|-----------|-----------------------------------|-------------------------------------------------------------------------------------------------|-----------------------------------------------------------------|

| 1.        | DC Power Supply<br>(Variable)     | Dual Output (e.g., +/- 12V<br>or +/- 15V for Op-Amps,<br>+5V for Digital ICs)                   | 1                                                               |

| 2.        | Digital Multimeter (DMM)          | Multi-function (Voltage,<br>Current, Resistance)                                                | 1                                                               |

| 3.        | Oscilloscope                      | Dual Trace, Minimum<br>20MHz Bandwidth                                                          | 1                                                               |

| 4.        | Breadboard                        | Standard Size, for circuit prototyping                                                          | 1                                                               |

| 5.        | Operational Amplifier<br>(Op-Amp) | LM741, TL082, or similar<br>general-purpose Op-Amp                                              | 2-3 (at least one<br>for DAC, one for<br>ADC if<br>implemented) |

| 6.        | Resistors (Carbon Film, 1/4W)     | R value (e.g., 1 k $\Omega$ to 10 k $\Omega$ ), 2R value (e.g., 2 k $\Omega$ to 20 k $\Omega$ ) | Assorted<br>(multiple of R<br>and 2R)                           |

| 7.        | Switches                          | DIP switches (e.g., 4-bit or 8-bit), or push buttons                                            | 1 (for DAC inputs)                                              |

| 8.  | LEDs                                  | Red, Green (for digital output indication in ADC)                                                         | 2-4                    |

|-----|---------------------------------------|-----------------------------------------------------------------------------------------------------------|------------------------|

| 9.  | Digital ICs (for ADC, if implemented) |                                                                                                           |                        |

|     | Logic Gates                           | e.g., 74LS04 (NOT),<br>74LS08 (AND), 74LS32<br>(OR) if building basic<br>logic from scratch<br>(Optional) | Assorted<br>(Optional) |

|     | Counter IC                            | e.g., 74LS93 (4-bit binary<br>counter) or 74LS193<br>(up/down counter)                                    | 1 (for ADC)            |

|     | Comparator IC                         | e.g., LM311, LM339<br>(single or quad<br>comparator)                                                      | 1 (for ADC)            |

| 10. | Connecting Wires                      | Breadboard jumper wires, various lengths                                                                  | Assorted               |

#### 4.0 THEORY AND FUNDAMENTALS:

This section provides a detailed theoretical background for DACs and ADCs, including all necessary formulas, principles, and in-depth explanations.

#### 4.1 Digital-to-Analog Converters (DACs)

Digital-to-Analog Converters (DACs) are essential components in systems that interface digital controllers (like microcontrollers or FPGAs) with the analog world (e.g., audio systems, motor control, display drivers). A DAC takes a digital input code (a binary number) and converts it into a proportional analog output voltage or current.

# 4.1.1 Key DAC Specifications

- Resolution: The smallest change in analog output voltage corresponding to a 1-bit change in the digital input. It is determined by the number of input bits (N). A higher number of bits means better resolution.

- Resolution = V\_FS/2N

- Where V\_FS is the full-scale output voltage (maximum possible analog output).

- Full-Scale Output Voltage (V\_FS): The maximum analog output voltage the DAC can produce.

- Reference Voltage (V\_REF): A stable, precise voltage source that the DAC uses to generate its analog output.

- Linearity: How closely the analog output tracks the ideal straight line relationship with the digital input.

- Monotonicity: An important characteristic where the analog output always increases or stays the same (never decreases) as the digital input code increases. All well-designed DACs should be monotonic.

- Settling Time: The time it takes for the analog output to settle to within a specified accuracy (e.g., 0.5 LSB) after a change in digital input.

#### 4.1.2 R-2R Ladder DAC

The R-2R ladder DAC is one of the most popular and practical DAC architectures due to its simplicity and the use of only two precise resistor values (R and 2R). This simplifies manufacturing compared to weighted resistor DACs which require a wide range of resistor values.

- Principle: It utilizes a network of resistors arranged in a ladder configuration where each digital input bit (D\_N-1, D\_N-2, ..., D\_0) controls a switch that connects either to a reference voltage (V\_REF) or to ground. The weighted current from each branch sums up at the input of an Op-Amp configured as a summing amplifier or current-to-voltage converter.

- Operation:

- Each branch of the R-2R ladder effectively contributes a current to the summing junction that is inversely proportional to a power of 2, corresponding to its bit position.

- For the Most Significant Bit (MSB, D\_N−1), the current contribution is I\_MSB=V\_REF/2R.

- For the next bit (D\_N-2), the current contribution is I\_N-2=V\_REF/4R, and so on.

- For the Least Significant Bit (LSB, D\_0), the current contribution is I\_LSB=V\_REF/(2NR).

- The Op-Amp sums these weighted currents and converts them into an output voltage.

- Output Voltage Formula (using an Op-Amp as an inverting summing amplifier):

V out=-R ftimesI total

- Where I\_total is the sum of currents from the ladder, and R\_f is the feedback resistor of the Op-Amp.

- If the Op-Amp is configured as an inverting summing amplifier with feedback resistor R f equal to 2R:

V\_out=-V\_REFtimesleft(fracD\_N-121+fracD\_N-222+cdots+fracD\_02Nright) Where D\_i is 1 if the bit is high, and 0 if low.

Note: If the switches connect to GND or V\_REF and the Op-Amp is non-inverting or uses a different reference point, the sign and exact scaling factor might change, but the proportional relationship remains. For a common configuration using switches to either ground or V\_REF and an Op-Amp in a non-inverting buffer configuration following the ladder, the output is directly proportional.

Numerical Example (3-bit R-2R DAC):

Let R=10kOmega, 2R=20kOmega, V\_REF=5V.

Using an Op-Amp as an inverting summing amplifier with R\_f=2R=20kOmega.

V\_out=-V\_REFtimesleft(fracD\_221+fracD\_122+fracD\_023right)

(Note: Often the formula is given as V\_out=-V\_REFtimesfrac12Nsum\_i=0N-1D\_i2i, with R\_f=R. Let's stick to the simpler practical formula for an inverting summer for clarity, assuming MSB at D\_2 corresponds to 22 weight, etc.).

A simpler way to consider the R-2R Ladder output before the Op-Amp (if the Op-Amp is a buffer) is:

V\_out=V\_REFtimesleft(fracD\_N-12+fracD\_N-24+cdots+fracD\_02Nright)

Let's use this common form where the ladder itself generates the weighted voltage, and an Op-Amp acts as a buffer.

For a 3-bit R-2R DAC: N=3. V\_out=V\_REFtimesleft(fracD\_22+fracD\_14+fracD\_08right)

If V\_REF=5V:

- Digital Input "000" (0): V\_out=5Vtimes(0)=0V

- Digital Input "001" (1): V\_out=5Vtimes(0/2+0/4+1/8)=5V/8=0.625V (This is 1 LSB)

- Digital Input "010" (2): V\_out=5Vtimes(0/2+1/4+0/8)=5V/4=1.25V

- Digital Input "111" (7):

V\_out=5Vtimes(1/2+1/4+1/8)=5Vtimes(4/8+2/8+1/8)=5Vtimes(7/8)=4.375V

Resolution = V\_FS/2N=5V/23=5V/8=0.625V.

#### 4.1.3 Weighted Resistor DAC (Optional)

- Principle: Each input bit controls a switch that connects a precisely weighted resistor to a summing junction, usually the inverting input of an Op-Amp summing amplifier. The resistor values are binary weighted (R,R/2,R/4,dots,R/2N-1).

- Output Voltage Formula (using Op-Amp inverting summing amplifier):

V\_out=-R\_ftimesV\_REFtimesleft(fracD\_N-1R\_0+fracD\_N-22R\_0+cdots+fracD\_02N-1R\_0right)

#### If R f=R 0:

V\_out=-V\_REFtimesleft(D\_N-1+fracD\_N-22+cdots+fracD\_02N-1right)

This formula looks slightly different from the R-2R in terms of power of 2, but the concept of weighted summation is the same. The weights are applied by the resistor values themselves.

#### • Comparison with R-2R:

- Component Requirements: Weighted resistor DACs require a wide range of precise resistor values (R,R/2,R/4,dots,R/2N-1). For high resolution (e.g., 10-bit), the smallest resistor might be R/512, which is very difficult to match accurately with the largest resistor R. The R-2R DAC only needs R and 2R resistors, making it much easier to fabricate and match precisely for high resolution.

- Performance: R-2R DACs generally offer better accuracy and linearity for higher resolutions due to their simpler resistor matching requirements.

#### 4.2 Analog-to-Digital Converters (ADCs)

Analog-to-Digital Converters (ADCs) are essential for converting real-world analog signals (like temperature, pressure, sound) into digital data that can be processed by microcontrollers, computers, or digital signal processors. An ADC takes an analog input voltage and converts it into a corresponding digital output code (binary number).

#### 4.2.1 Key ADC Specifications

- Resolution: The smallest change in analog input voltage that can be detected and converted to a 1-bit change in the digital output. Similar to DAC, higher bits mean better resolution.

- Resolution = V\_FS/2N

- Where V\_FS is the full-scale input voltage range the ADC can handle.

- Conversion Time: The time it takes for the ADC to complete one conversion from analog input to digital output. This is a critical parameter for speed.

- Quantization Error: The inherent error due to the conversion of a continuous analog signal into a discrete digital code. The maximum quantization error is typically pm1/2 LSB.

- Sampling Rate: How many conversions per second the ADC can perform.

#### 4.2.2 Single-Slope ADC (Ramp ADC or Integrating ADC)

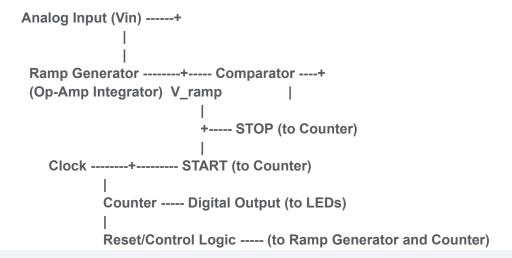

- Principle: A single-slope ADC works by comparing the analog input voltage (V\_in) with a linearly increasing ramp voltage. A counter starts counting when the ramp begins, and stops when the ramp voltage equals the input voltage.

The final count is proportional to the input voltage.

- Components:

- 1. Ramp Generator: Typically an Op-Amp integrator that generates a linear ramp voltage when a constant current charges a capacitor.

- Output of Integrator: V\_ramp(t)=-frac1RCintV\_in\_integratordt. If

V\_in\_integrator is a constant voltage, V\_ramp(t) is a linear ramp.

- 2. Comparator: Compares the analog input voltage (V\_in) with the ramp voltage (V\_ramp). Its output goes high when V\_ramp exceeds V\_in.

- 3. Counter: A digital counter (e.g., binary counter) that is enabled by a control signal and counts clock pulses.

- 4. Control Logic: Logic to start the ramp and counter, stop the counter when the comparator switches, and reset for the next conversion.

- Conversion Process:

- 1. The capacitor in the ramp generator is discharged to zero. The counter is reset to zero.

- 2. At the start of conversion, a constant current (or voltage) is applied to the integrator, causing the ramp voltage to increase linearly from 0V.

- 3. Simultaneously, the counter starts counting clock pulses.

- 4. When the ramp voltage (V\_ramp) equals the analog input voltage (V\_in), the comparator output changes state.

- 5. This comparator output change stops the counter.

- 6. The final count stored in the counter is the digital representation of the analog input voltage.

- Advantages: Simple to implement, low cost.

- Disadvantages: Slow conversion time (depends on the maximum ramp voltage and clock frequency), accuracy can be affected by variations in the ramp slope (R, C, and voltage source stability).

Numerical Example (Single-Slope ADC):

Assume a ramp generator that generates 1V/ms. A 4-bit ADC (24=16 quantization levels). Max input voltage V\_FS=5V.

Resolution = 5V/16=0.3125V.

If V\_in=2.5V, the ramp needs to reach 2.5V. This takes 2.5V/(1V/ms)=2.5ms.

If the clock frequency for the counter is 10 kHz (100 µs per pulse):

Number of clock cycles = 2.5ms/100µs=25 cycles.

The digital output would correspond to 25. This is usually normalized to fit the 4-bit range (0-15). The count needs to be scaled correctly by the max count and max voltage.

A more direct relationship: Digital Output Count =fracV\_inV\_max\_ramptimestextMaxCount

If Max Count for 4-bit is 15 (for 0-15 range), and V\_max\_ramp is set to V\_FS=5V.

Digital Output Count = frac2.5V5Vtimes15=0.5times15=7.5. This would be rounded to 7 or 8.

#### 4.2.3 Successive Approximation ADC (SAR ADC) (Conceptual)

- Principle: A SAR ADC performs a binary search to find the digital code that best represents the analog input voltage. It uses a DAC, a comparator, and a successive approximation register (SAR) control logic.

- Conversion Process (for N bits):

- 1. The SAR sets the MSB (D\_N-1) of the internal DAC to '1' and all other bits to '0'.

- 2. The DAC converts this code to an analog voltage.

- 3. The comparator compares the analog input (V\_in) with the DAC output.

- 4. If V\_in is greater than the DAC output, the MSB remains '1'. Otherwise, it is set to '0'.

- 5. The SAR then moves to the next bit (D\_N-2), sets it to '1', and repeats the comparison process.

- 6. This process continues for each bit, from MSB to LSB. After N comparisons, the SAR contains the final N-bit digital output code.

- Advantages: High speed (converts in N clock cycles, where N is the number of bits), good accuracy, widely used.

- Disadvantages: Requires a precise internal DAC, resolution limited by DAC resolution.

Numerical Example (3-bit SAR ADC, V\_FS=5V, 1 LSB = 0.625V):

Let V\_in=3.5V.

- Trial 1 (MSB, D\_2): Set D\_2=1,D\_1=0,D\_0=0. DAC Output = 5Vtimes(1/2+0/4+0/8)=2.5V.

- Compare: V\_in(3.5V) DAC Output (2.5V) implies D\_2 remains 1. Current Code: "100".

- Trial 2 (Next bit, D\_1): Keep D\_2=1. Set D\_1=1,D\_0=0. DAC Output = 5Vtimes(1/2+1/4+0/8)=5Vtimes(0.75)=3.75V.

- Compare: \$V\\_{in} (3.5V) \<\$ DAC Output (3.75V) implies D\_1 set to 0.</li>

Current Code: "100".

- Trial 3 (LSB, D\_0): Keep D\_2=1,D\_1=0. Set D\_0=1. DAC Output = 5Vtimes(1/2+0/4+1/8)=5Vtimes(0.625)=3.125V.

- Compare: V\_in(3.5V) DAC Output (3.125V) implies D\_0 remains 1. Final Code: "101".

- Final Digital Output: "101" (decimal 5). Corresponding analog value is 5times(5/8)=3.125V.

- Note: 3.5V is rounded to 3.125V. This illustrates quantization error.

#### 4.2.4 Switched Capacitor Integrator (Optional/Advanced)

Principle: In integrated circuits, large precise resistors and capacitors are difficult to fabricate. Switched capacitor (SC) circuits overcome this by using small capacitors, Op-Amps, and analog switches (MOSFETs acting as switches) driven by a clock. They mimic the behavior of resistors by switching a capacitor between voltage nodes.

- Operation (Resistor Emulation): A capacitor (C\_S) is rapidly switched between an input voltage and a summing junction. When connected to the input, it charges to the input voltage. When connected to the summing junction, it discharges, transferring a charge packet. The average current transferred is proportional to the input voltage and switching frequency. This current effectively mimics a resistor with resistance R\_eq=1/(f\_CLKtimesC\_S).

- SC Integrator: By replacing the input resistor of a continuous-time Op-Amp integrator with a switched capacitor "resistor", a discrete-time integrator is formed.

- Output Voltage: V\_out(k)=V\_out(k-1)-fracC\_SC\_FV\_in(k-1)

- Where C\_S is the sampling capacitor, C\_F is the feedback capacitor.

- Advantages in IC Design:

- Area Saving: Capacitors are much smaller than high-value resistors in ICs.

- Accuracy/Matching: Ratios of capacitors can be precisely matched, leading to accurate filter characteristics or gain values, even if individual capacitor values vary.

- Programmability: Filter cutoff frequencies or gain can be easily controlled by changing the clock frequency.

- Process Compatibility: Easier to implement in standard CMOS processes.

#### **5.0 CIRCUIT DIAGRAMS:**

Figure 9.1: 3-bit R-2R Ladder DAC with Op-Amp Buffer

```

|

Vout (Buffered Analog Output)

Op-Amp Power: +Vcc and -Vee (e.g., +/-12V)

```

Note on R-2R construction: Each 'digital input bit' (D0, D1, D2) connects to a 2R resistor. The other end of this 2R resistor connects to the common ladder rail. From the junction of each 2R and the rail, an R resistor connects to the next stage. The final R resistor connects to ground. This design produces a voltage at the end of the ladder.

Figure 9.2: Op-Amp Integrator (for Single-Slope ADC Ramp Generator)

```

+Vcc (e.g., +12V)

|

Op-Amp (e.g., LM741)

Non-inverting Input (+) --- GND

|

+-- Rf (Feedback Resistor, optional for discharge)

|

Inverting Input (-) ---+---- Cin (Input Capacitor) ---- Vin (Constant Voltage, e.g., +5V or -5V)

|

+-- Cf (Feedback Capacitor) ---- Output of Op-Amp (V_ramp)

-Vee (e.g., -12V)

```

For ramp generation: Vin is a constant voltage. A switch in parallel with Cf (not shown) is often used to discharge Cf to reset the integrator.

Figure 9.3: Basic Single-Slope ADC (Conceptual Block Diagram)

#### 6.0 PROCEDURE:

Follow these systematic steps to design, build, and characterize the DAC and conceptually understand the ADCs.

#### Part A: R-2R Ladder DAC Construction and Characterization

- 1. R-2R Ladder Design (3-bit or 4-bit):

- Resolution: Decide on 3-bit or 4-bit (3-bit is simpler for initial build).

- $\circ$  Resistor Values: Choose a standard resistor value for 'R' (e.g., 1 k $\Omega$ , 2.2 k $\Omega$ , or 4.7 k $\Omega$ ). Then calculate '2R'. Ensure you have enough of both values. Good quality, low tolerance resistors (e.g., 1% metal film) are recommended for better accuracy.

- Reference Voltage (V\_REF): Use a stable DC power supply voltage (e.g., +5V).

- Op-Amp Configuration: Use an Op-Amp (e.g., LM741) as a voltage follower (buffer) at the output of the R-2R ladder to provide low output impedance and prevent loading effects. Power the Op-Amp with +/- 12V or +/- 15V.

- Pre-Calculations: For your chosen R-2R design, calculate the expected analog output voltage for all possible digital input combinations (from 000 to 111 for 3-bit, or 0000 to 1111 for 4-bit). Calculate the LSB voltage and Full-Scale Voltage. Record these in Table 7.1.

#### 2. Circuit Construction:

- Assemble the R-2R ladder network on the breadboard. Pay careful attention to connecting resistors correctly (R and 2R values).

- Connect the digital input lines (corresponding to D0, D1, D2, etc.) to switches (DIP switches are ideal, connecting to V\_REF for '1' and GND for '0').

- Connect the output of the R-2R ladder to the non-inverting input of the Op-Amp configured as a voltage follower.

- Connect the Op-Amp to its dual power supply.

- 3. Measurement and Transfer Characteristic Plotting:

- Apply the reference voltage (V\_REF) to the R-2R ladder.

- For each possible digital input combination (e.g., starting from 000, then 001, 010, ..., up to 111 for 3-bit):

- Set the DIP switches to the desired digital input code.

- Measure the analog output voltage (V\_out) from the Op-Amp buffer using the DMM.

- Record the digital input and corresponding measured analog output voltage in Table 7.2.

- After collecting all data, plot the transfer characteristic: Digital Input (decimal value) on the X-axis vs. Analog Output Voltage (Y-axis). This should ideally be a straight line.

#### Part B: Weighted Resistor DAC (Optional)

1. Weighted Resistor DAC Design (3-bit):

- Reference Voltage: Use the same V REF (e.g., +5V).

- $\circ$  Resistor Values: Choose an input resistor R\_0 for the MSB (e.g., 10 k $\Omega$ ). Then calculate the required resistor values for the other bits: 2R\_0 for the next bit, 4R\_0 for the LSB (for 3-bit example).

- Op-Amp Configuration: Use an Op-Amp as an inverting summing amplifier. Choose a feedback resistor R\_f (e.g., R\_f=R\_0).

- 2. Circuit Construction & Measurement:

- Assemble the weighted resistor DAC circuit.

- Connect digital input switches to apply V\_REF (for '1') or GND (for '0') to the weighted resistors.

- Measure the analog output voltage for all possible digital input combinations. Record in Table 7.3.

#### 3. Comparison:

- Compare the components required for this DAC vs. the R-2R DAC.

- Discuss the challenges in selecting and matching resistor values, especially for higher bit resolutions.

#### Part C: Single-Slope ADC (Conceptual/Basic Implementation)

- 1. Understand the Principle: Review the theory of Single-Slope ADCs (Section 4.2.2). Focus on the roles of the ramp generator, comparator, and counter.

- 2. Basic Ramp Generator (Op-Amp Integrator):

- Design: Construct an Op-Amp integrator as per Figure 9.2. Choose R and C values to generate a relatively slow, linear ramp (e.g., R=10kOmega, C=0.1muF). Apply a constant DC input voltage (V\_in\_integrator, e.g., -1V for a positive going ramp if Op-Amp is inverting integrator).

- Observation: Apply power. Observe the ramp voltage on the oscilloscope. It should increase linearly over time. Identify how to reset it (e.g., briefly shorting the capacitor, or using a reset switch).

- 3. Comparator Functionality:

- Design: Connect an Op-Amp (or dedicated comparator IC like LM311) as a comparator. Connect V\_ramp to one input and a fixed analog input voltage (V in) to the other input.

- Observation: Observe the comparator output on the oscilloscope as the ramp voltage increases and crosses the fixed analog input voltage. The output should sharply switch states.

- 4. Qualitative Demonstration of Conversion (if full implementation is challenging):

- Conceptual: Discuss how the counter would be started when the ramp begins and stopped by the comparator output. The final count represents the analog input.

- Basic Implementation (if time and components allow):

- Connect the ramp generator output to one input of the comparator.

- Connect a variable DC voltage (Analog Input, V\_in) to the other input of the comparator.

- Set up a simple 4-bit counter (e.g., 74LS93 or 74LS193) with LEDs connected to its output bits.

- Use a push-button switch for "Start Conversion" (resets counter, enables ramp).

- Use the comparator output to "Stop" (latch) the counter.

- Demonstrate: For a given V\_in, initiate conversion. Observe the LEDs count up until the comparator switches, then they should hold the final digital code. Vary V\_in and observe the change in the final digital count.

- Record qualitative observations in Table 7.4.

#### Part D: Successive Approximation ADC (Conceptual/Simulation)

- 1. Understand the Principle: Thoroughly review the theory of SAR ADCs (Section 4.2.3). Understand its binary search algorithm.

- 2. Conceptual Discussion:

- Discuss how the SAR ADC achieves its speed advantage compared to the single-slope ADC.

- Identify the main components (DAC, comparator, SAR logic) and their interaction.

- Trace the conversion steps for a few example analog input voltages for a small bit resolution (e.g., 3-bit).

- 3. Simulation (If available and feasible):

- If you have access to circuit simulation software (e.g., LTSpice, Multisim, Proteus), try to find or build a simple SAR ADC model.

- Run simulations with varying analog input voltages and observe the bit-by-bit conversion process.

- Record observations or simulation waveforms. (This part is primarily for deeper understanding if practical build is not possible).

#### Part E: Switched Capacitor Integrator (Optional/Advanced)

- 1. Understand the Principle: Review the theory of switched capacitor circuits and their use in integrators (Section 4.2.4).

- 2. Basic SC Integrator Construction (If components available):

- Components: You would need an Op-Amp, two capacitors (C\_S,C\_F), and at least two analog switches (e.g., CD4066 quad analog switch IC).

You also need a two-phase non-overlapping clock generator (e.g., using 555 timers or logic gates) to control the switches.

- Circuit: Build a basic SC integrator. Apply a square wave clock to the switches. Apply a DC input voltage.

- Observation: Observe the output on the oscilloscope. It should integrate

the input voltage, similar to a continuous-time integrator, but with

discrete voltage steps corresponding to clock cycles. Vary the clock

frequency or input voltage and observe the effect on the integration

rate.

- 3. Discussion:

- Compare the SC integrator's behavior to a continuous-time Op-Amp integrator.

- Discuss the primary advantages of switched capacitor circuits in integrated circuit design, particularly concerning resistor replacement, accuracy, and programmability.

# 7.0 OBSERVATIONS AND READINGS:

# 7.1 R-2R Ladder DAC Design Parameters:

| Parameter                               | Value Selected/Designed | Remarks/Comparison |

|-----------------------------------------|-------------------------|--------------------|

| Number of Bits (N)                      | bit(s)                  | (e.g., 3 or 4)     |

| Resistor 'R' value                      | Ω                       |                    |

| Resistor '2R' value                     | Ω                       |                    |

| Reference Voltage<br>(V_REF)            | v                       |                    |

| Op-Amp Power Supply                     | +v/-                    |                    |

| Calculated LSB Voltage<br>(Resolution)  | v                       |                    |

| Calculated Full-Scale<br>Voltage (V_FS) | v                       |                    |

7.2 R-2R Ladder DAC Transfer Characteristic Data:

| Digital<br>Input (D2<br>D1 D0 for<br>3-bit) | Digital<br>Input<br>(Decimal) | Expected Analog Output (V_out) (V) | Measured<br>Analog Output<br>(V_out) (V) | Discrepancy<br>(Measured -<br>Expected) (V) |

|---------------------------------------------|-------------------------------|------------------------------------|------------------------------------------|---------------------------------------------|

| 000                                         | 0                             |                                    |                                          |                                             |

| 001                                         | 1                             |                                    |                                          |                                             |

| 010                                         | 2                             |                                    |                                          |                                             |

| 011                                         | 3                             |                                    |                                          |                                             |

| 100                                         | 4                             |                                    |                                          |                                             |

| 101                                         | 5                             |                                    |                                          |                                             |

| 110                                         | 6                             |                                    |                                          |                                             |

| 111                                         | 7                             |                                    |                                          |                                             |

| (Add<br>more<br>rows if<br>4-bit<br>DAC)    |                               |                                    |                                          |                                             |

# 7.3 Weighted Resistor DAC Data (Optional):

| Parameter | Value Selected/Designed | Remarks/Comparison |

|-----------|-------------------------|--------------------|

|           |                         |                    |

| Number of Bits (N)        | bit(s) | (e.g., 3)    |

|---------------------------|--------|--------------|

| Resistor R_0 (for MSB)    | Ω      |              |

| Resistor for D_1          | Ω      | (e.g., 2R_0) |

| Resistor for D_0 (LSB)    | Ω      | (e.g., 4R_0) |

| Feedback Resistor (R_f)   | Ω      |              |

| Reference Voltage (V_REF) | v      |              |

| Digital Input<br>(D2 D1 D0 for<br>3-bit) | Digital Input<br>(Decimal) | Expected Analog<br>Output (V_out) (V) | Measured Analog<br>Output (V_out) (V) |

|------------------------------------------|----------------------------|---------------------------------------|---------------------------------------|

| 000                                      | 0                          |                                       |                                       |

| 001                                      | 1                          |                                       |                                       |

| 010                                      | 2                          |                                       |                                       |

| 011                                      | 3                          |                                       |                                       |

| 100                                      | 4                          |                                       |                                       |

| 101 | 5 |  |

|-----|---|--|

| 110 | 6 |  |

| 111 | 7 |  |

#### 7.4 Single-Slope ADC Observations (Qualitative):

| Component/Phase                       | Observation                                                               |

|---------------------------------------|---------------------------------------------------------------------------|

| Ramp Generator (Op-Amp<br>Integrator) | (Describe linearity, slope, and max voltage of the generated ramp.)       |

| Comparator Functionality              | (Describe how the comparator output switches when V_ramp crosses V_in.)   |

| ADC Conversion Process (Qualitative)  | (Describe observed counter behavior, how it stops, and relation to V_in.) |

| Effect of varying V_in                | (Describe how changing analog input affects the final digital count.)     |

# 8.0 GRAPHS:

Include relevant graphs based on your experimental data. Use appropriate labels and scales.

- Graph 9.1: R-2R Ladder DAC Transfer Characteristic

- Type: Linear plot.

- Plot: Digital Input (Decimal Value) on the X-axis vs. Measured Analog Output Voltage (Y-axis).

- Markings: Plot both the ideal (expected) and measured points. Draw a straight line connecting the ideal points.

#### 9.0 CALCULATIONS:

Provide detailed steps for all calculations performed in this experiment, using your measured values where appropriate.

#### 9.1 R-2R Ladder DAC Calculations:

- LSB Voltage (Resolution):

V\_LSB=V\_REF/2N = [Your Calculation] V

- Expected Analog Output Voltage for a given Digital Input:

V\_out=V\_REFtimesleft(fracD\_N-12+fracD\_N-24+cdots+fracD\_02Nright)

(Show one example calculation for a specific digital input, e.g., "101")

#### 9.2 Weighted Resistor DAC Calculations (Optional):

Expected Analog Output Voltage for a given Digital Input (assuming R\_f=R\_0 and inverting Op-Amp):

V\_out=-V\_REFtimesleft(D\_N-1+fracD\_N-22+cdots+fracD\_02N-1right) (Show one example calculation for a specific digital input, e.g., "101")

#### 10.0 RESULTS:

Summarize your key findings from the experiment, presenting both measured and calculated parameters.

- R-2R Ladder DAC:

- Number of bits: [Your Value]

- Designed LSB Voltage: [Your Value] V

- Observed Linearity: [Good/Fair/Poor based on discrepancy]

- Full-Scale Output Voltage: [Your Value] V (measured)

- Weighted Resistor DAC (Optional):

- Qualitative comparison with R-2R: [Briefly state observations on component requirements and relative accuracy challenges.]

- Single-Slope ADC (Qualitative):

- Observed ramp generation: [Briefly describe, e.g., "Linear ramp observed."]

- Observed comparator action: [Briefly describe, e.g., "Sharp switching observed."]

- Observed conversion process: [Briefly describe, e.g., "Counter correctly stopped by comparator, indicating digital representation."]

- Successive Approximation ADC (Conceptual):

- Principle understood: [Confirm understanding, e.g., "Binary search process clearly understood."]

- Speed Advantage: [Confirm understanding, e.g., "Recognized as a fast conversion method."]

- Switched Capacitor Integrator (Optional/Advanced):

- Observed behavior: [Briefly describe if implemented, e.g., "Discrete-time integration observed."]

Advantages: [List key advantages in IC design, e.g., "Area saving, better matching, programmability."]

#### 11.0 DISCUSSION AND ANALYSIS:

This is a crucial section for interpreting your results, comparing them with theoretical expectations, explaining observed phenomena, and discussing any discrepancies.

#### 1. R-2R Ladder DAC Analysis:

- Transfer Characteristic: Discuss the linearity of your measured transfer characteristic. How well did your measured output voltages match the expected values? What was the maximum discrepancy?

- Sources of Error: Identify the primary sources of error in the R-2R ladder DAC performance (e.g., resistor tolerances, Op-Amp offset voltage and bias currents, non-ideal switches, loading effects of the DMM). Explain how these errors affect the accuracy and linearity.

- Advantages of R-2R: Explain why the R-2R ladder is preferred over the weighted resistor DAC, particularly for higher bit resolutions, in terms of resistor matching and ease of fabrication.

- Importance: Discuss the practical applications of DACs (e.g., audio playback, signal generation, motor control).

#### 2. Weighted Resistor DAC Comparison (Optional):

- Discuss the challenges in building a weighted resistor DAC, particularly regarding the wide range of precise resistor values required.

- Explain why matching these resistor values accurately becomes extremely difficult for DACs with more than a few bits of resolution, leading to linearity issues.

#### 3. Single-Slope ADC Analysis:

- Working Principle: Elaborate on the detailed operation of the single-slope ADC, explaining the role of each component (ramp generator, comparator, counter, control logic) in the conversion process.

- Advantages and Disadvantages: Discuss the advantages (simplicity, low cost) and significant disadvantages (slow conversion time, sensitivity to component drift in ramp generator) of this ADC architecture.

- Factors Affecting Accuracy: Explain how the stability of the ramp generator (Op-Amp integrator), clock frequency, and comparator characteristics affect the accuracy and resolution of the single-slope ADC.

#### 4. Successive Approximation ADC (SAR ADC) Discussion:

- Binary Search Algorithm: Explain in detail how the SAR ADC uses a binary search algorithm (trial and error, bit by bit from MSB to LSB) to achieve faster conversion.

- Speed vs. Complexity: Compare the speed of SAR ADCs with single-slope ADCs. Discuss the trade-off in terms of circuit complexity (requiring a DAC and SAR logic).

- Applications: Mention common applications where SAR ADCs are widely used (e.g., data acquisition systems, medical instrumentation, general-purpose microcontrollers).

- 5. Switched Capacitor Integrator (Optional/Advanced):

- Continuous vs. Discrete Time: Discuss the fundamental difference between a continuous-time Op-Amp integrator and a switched capacitor integrator.

- Emulating Resistors: Explain how switched capacitors effectively "mimic" resistors, providing an equivalent resistance controlled by switching frequency and capacitance.

- IC Advantages: Elaborate on why switched capacitor circuits are highly advantageous in integrated circuit design, emphasizing area reduction, ratio matching accuracy, and ease of programmability compared to traditional resistor-based designs.

#### 12.0 CONCLUSION:

Conclude your experiment by summarizing the key learning outcomes and reinforcing the understanding gained.

This experiment provided a practical and conceptual understanding of Digital-to-Analog (DAC) and Analog-to-Digital (ADC) conversion, which are fundamental to mixed-signal systems. We successfully constructed and characterized an R-2R ladder DAC, verifying its linear transfer characteristic and appreciating its advantages in terms of ease of resistor matching for practical implementations. While the weighted resistor DAC was explored conceptually, its practical limitations for high resolution became evident. Furthermore, the experiment elucidated the working principles of the single-slope ADC, highlighting its simplicity versus its speed limitations and dependence on component stability. The successive approximation ADC was understood as a more advanced, faster conversion technique utilizing a binary search. Finally, the optional exploration of the switched capacitor integrator offered insights into advanced techniques for integrated circuit design, particularly for overcoming the challenges of precise resistor fabrication. Overall, this experiment has provided a solid foundation for comprehending the core concepts and various architectures employed in modern data conversion systems.